- How To Open Pcb File In Allegro Car

- How To Open Pcb File In Allegro Software

- How To Open .pcb File In Allegro

How To Open Pcb File In Allegro Car

You use the transfer (pst) files generated by the DE CIS Create Netlist command to transfer information from the schematic to a OrCAD and Allegro PCB Editor design. These files are:

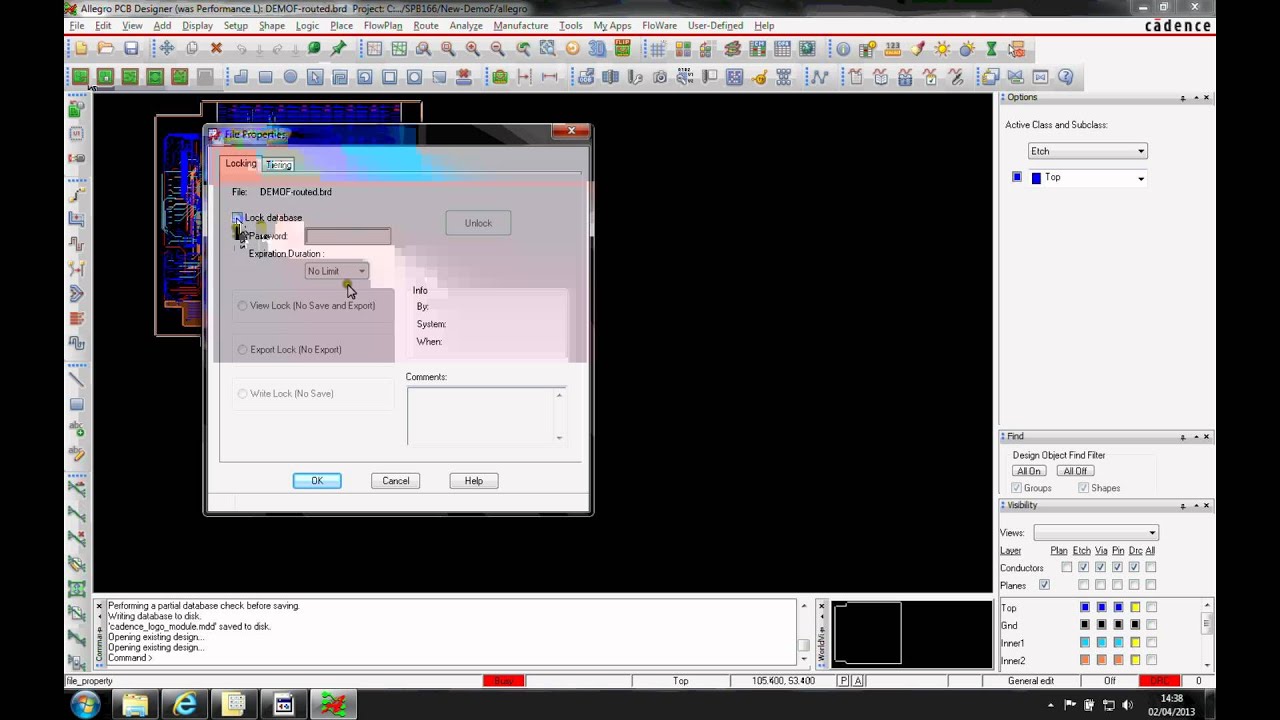

Allegro PCB Design SKILL Tutorial In the previous tutorial we gave the commands in a command line and saw the results in a command line window. It is possible to put all the commands in a file ( typically with extension.il) and then load the file from the command line. Let us say the content lf the file hello.il is for( i 1 3 print( 'hello' )). Netlister inside DE CIS, you can import the interface files from within OrCAD and Allegro PCB Editor. Use the File - Import - Logic command from the top menu in OrCAD and Allegro PCB Editor and choose the DE CIS option. Use the Import From field to point to the three interface files created by the DE CIS -Allegro PCB Editor Netlister program. Allegro PCB Design SKILL Tutorial In the previous tutorial we gave the commands in a command line and saw the results in a command line window. It is possible to put all the commands in a file ( typically with extension.il) and then load the file from the command line. Let us say the content lf the file hello.il is for( i 1 3 print( 'hello' )).

Description |

|---|

This is a parts list file. It lists each physical package (created by the packager) in the schematic, along with its reference designator and device type. For packages comprised of multiple logic gates, this file identifies which gate was placed in which section of the physical package. This file may also contain some properties attached to parts in the schematic, such as ROOM=’IF’, VALUE=’4.7K’. |

This is a netlist file. It uses keywords (net_name, node_name) to specify the reference designators and pin numbers associated with each net in the schematic. This file may also contain some properties attached to nets in the schematic, such as ROUTE_PRIORITY, ECL, and so forth. |

This is a device definition file. It contains electrical characteristics (for example, pin direction and loading), logical-to-physical pin mapping, and voltage requirements. It defines the number of gates in a device, including gate and pin swapping information. This file also contains the name of the package symbol that represents this device type in the physical layout (such as JEDEC_TYPE=’DIP14_3’, ALT_SYMBOLS=’(T:SOIC14)’). |

How To Open Pcb File In Allegro Software